| PREPARED BY: | DATE |                                      | SPEC No. LC96211                            |  |

|--------------|------|--------------------------------------|---------------------------------------------|--|

|              |      | SHARP                                | FLLE Na                                     |  |

|              |      |                                      | ISSUED FEB., 26, 1996                       |  |

| APPROVED BY: | DATE | LIQUID CRYSTAL DISPLAY <b>GROU</b> I | PAGE 25 Pages                               |  |

|              |      | SHARP CORPORATION                    | APPLICABLE DIVISION                         |  |

| _            |      |                                      | <b>DUTY</b> PANEL DEVELOPMENT <b>CENTER</b> |  |

|              |      |                                      | ☐TFT DEVELOPMENT CENTER                     |  |

|              |      |                                      | ☐LCD PRODUCTS DEVELOPMENT                   |  |

|              |      | SPECIFICATION                        | CENTER                                      |  |

|              |      |                                      | ☐ IEL PRODUCTION DEPT.                      |  |

|              |      |                                      |                                             |  |

|              |      |                                      |                                             |  |

|              |      |                                      |                                             |  |

|              |      |                                      |                                             |  |

Device specification for Passive Matrix LCD module

Model No.

LM64K103

□ I CUSTOMER' S APPROVAL

ВУ

DATE

PRESENTED Juone

Y. Inoue

Department General Manager Engineering Department 2 DUTY Panel Development center LCD GROUP

| SPEC No. | MODEL No. | PAGE |

|----------|-----------|------|

| LC96211  | LM64K103  | 1    |

1. Application

This data sheet is to introduce the specification of LM64K103, Passive Matrix type LCD Module

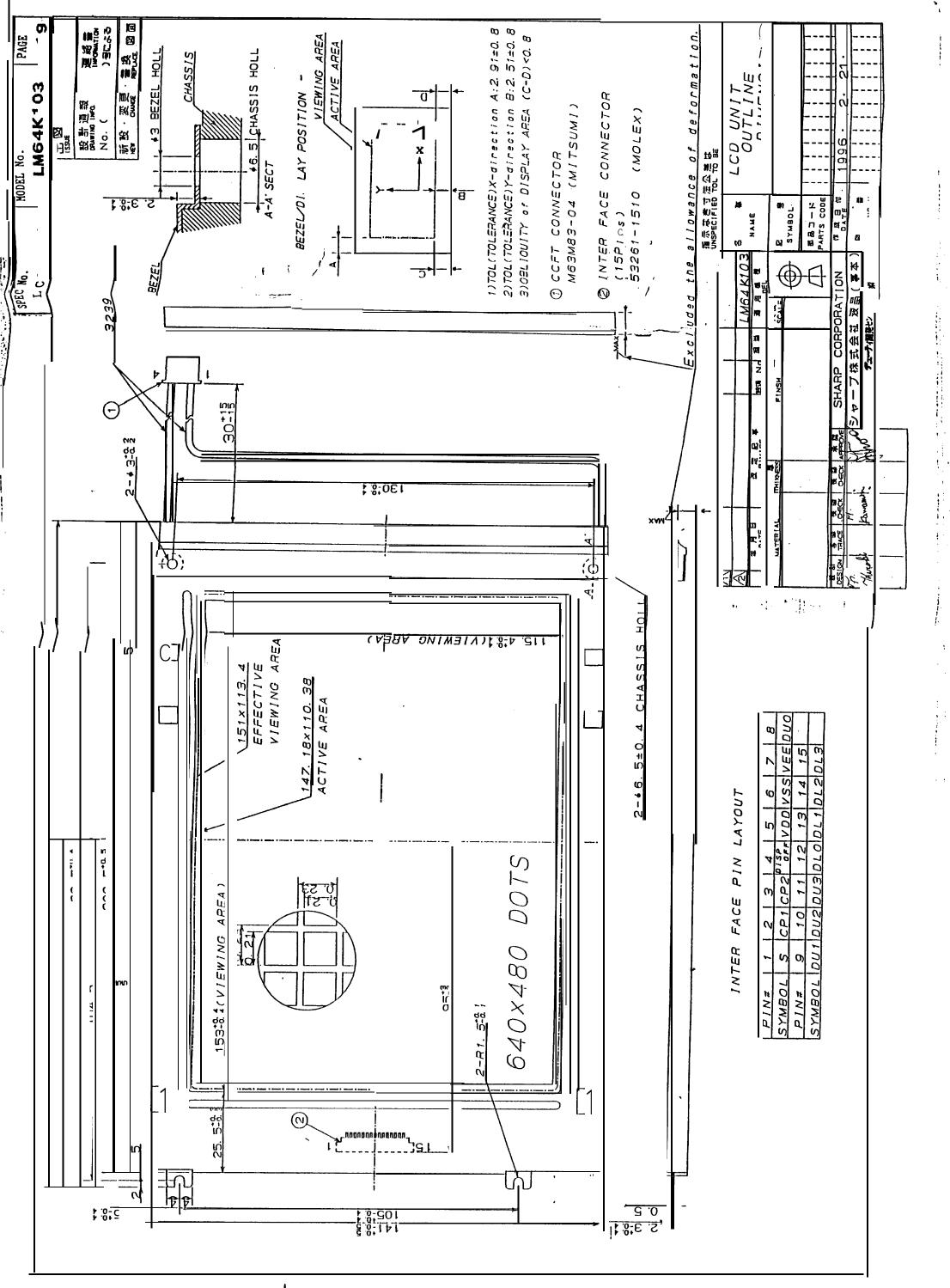

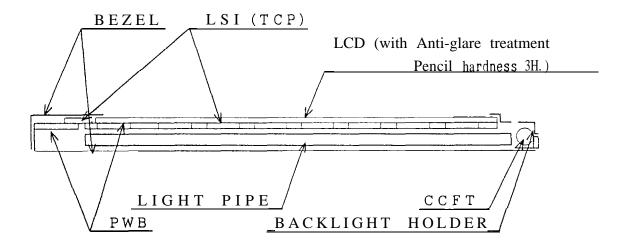

2. Construction and Outline

Construction:640 X480 dots display unit consisting of an LCD panel,

PWB(printed wiring board) with electric components

mounted onto,TCP(tape carrier Package) to connect the LCD panel

and PWB electrically, and plastic chassis with CCFT backlight

and bezels to fix them mechanically.

Outline : See Fig. 10

Connection : See Fig. 10 and Table 6

| SPEC No. | MODEL No. |

|----------|-----------|

| LC96211  | L M 6 4   |

MODEL No. PAGE

LM64K103

2

## SHARP

# 3. Mechanical Specifications

Table 1

| Parameter              | Specifications                         | Module |

|------------------------|----------------------------------------|--------|

| Outline dimensions     | $200,5(W) X141 (H) \times 7MAX(D)*1*2$ | mm     |

| Effective viewing Area | 151( W) X113,4(H)                      | mm     |

| Display format         | 640(W) X480(H) full dot                | _      |

| Dot size               | 0.21X0.21                              | mm     |

| Dot spacing            | 0.02                                   | mm     |

| Dot color              | Black*3*4                              | _      |

| Background color       | White*3*4                              | _      |

| Weight                 | Approx. 260                            | g      |

- \*1 Excluded the mounting tabs.

- \*2 Excluded the allowance of deformation.

- \*3 Due to the characteristics of the LC material, the colors vary with environmental temperature.

- \*4 Positive-type display

Displayed data "H": Dots ON: Black Displayed data "L": Dots OFF: White

- 4. Absolute Maximum Ratings

- 4-1 Electrical absolute maximum ratings

Table 2

| Parameter                  | Symbol                           | MIN. | MAX.             | Unit | Remark   |

|----------------------------|----------------------------------|------|------------------|------|----------|

| Supply voltage (Logic)     | V <sub>DD</sub> -V <sub>SS</sub> | 0    | 6.0              | V    | Ta=25 "C |

| Supply voltage (LCD drive) | V <sub>DD</sub> -V <sub>EE</sub> | 0    | 28,0             | V    | Ta=25 "C |

| Input voltage              | VIN                              | 0    | V <sub>D</sub> D | V    | Ta=25 °C |

| SPEC No. | MODEL No. | PAGE |

|----------|-----------|------|

| LC96211  | LM64K103  | 3    |

## 4-2 Environmental Conditions

#### Table 3

| 14010-5             |        |        |               |        |                                    |  |  |

|---------------------|--------|--------|---------------|--------|------------------------------------|--|--|

| I tern              | Tstg   |        | Topr          |        | Remark                             |  |  |

|                     | MIN.   | MAX .  | MIN.          | MAX.   |                                    |  |  |

| Ambient temperatuer | -25 'C | +70 "c | 0 "C          | +50 "c | Note 4                             |  |  |

| Humidity            | Note 1 |        | Note 1        |        | No condensation                    |  |  |

| Vibration           | Note 2 |        | Note 2        |        | 3 directions (X/Y/2)               |  |  |

| Shock               | Note 3 |        | Note 3 Note 3 |        | 6 directions $(\pm X \pm Y \pm Z)$ |  |  |

Note 1) Ta  $\leq$  40 °C ... ..95 % RH Max Ta>40 °C ... .. Absolute humidity shall be less than Ta=40 °C/95 % RH.

Note 2) These test condition are in accordance with "IEC 68-2-6".

| Frequency       | 10 Hz∼57 Hz | 57 Hz-500 Hz               |

|-----------------|-------------|----------------------------|

| Vibration level | _           | 9.8 m/s <sup>2</sup> (1 G) |

| Vibration width | 0.075 mm    | _                          |

| Interval        | 5 Hz∼500 H  | z-5 Hz/n min               |

2 hours for each direction of X/Y/Z (6 hours as total)

Note 3) Accerelation: 490 m/s<sup>2</sup>

Pulse width: 11 ms

3 times for each direction of  $\pm X/\pm Y/\pm Z$

Note 4) Care should be taken so that the LCD Module may not be subjected to the temperature out of this specification.

| SPEC No.        | MODEL No. | PAGE |

|-----------------|-----------|------|

| 1 7 7 9 6 2 1 1 | LMGAV100  | 1 4  |

5. Electrical Specifications

5-1 Electrical characteristics

Tabel 4 Ta=25 "C

| Parameter                  | Symbol                           | Conditions      | Min.                | TYP. | Max.                | Unit |

|----------------------------|----------------------------------|-----------------|---------------------|------|---------------------|------|

| Supply voltage (Logic)     | V <sub>DD</sub> -V <sub>ss</sub> |                 | 2.7                 | 3.0  | 5.5                 | V    |

| Supply voltage (LCD drive) | V <sub>DD</sub> -V <sub>EE</sub> | Note 1) Note 2) | 18.4                | 22.0 | 26.4                | V    |

| Input signal voltage       | V 1 N                            | "H" level       | 0.8 V <sub>DD</sub> | -    | V <sub>DD</sub>     | V    |

|                            |                                  | "L" level       | 0                   | -    | 0.2 V <sub>DD</sub> | V    |

| Input leakage current      | III                              | "H" level       | _                   | _    | 250                 | μA   |

|                            |                                  | "L" level       | -250                | _    | 1                   | μA   |

| Supply current (Logic)     | IDD                              |                 | -                   | 21   | 29                  | mA   |

| Supply currect (LCD dirve) | IEE                              | Note 3)         | _                   | 20   | 28                  | mA   |

| Power consumption          | Pd                               |                 | _                   | 450  | 600                 | mW   |

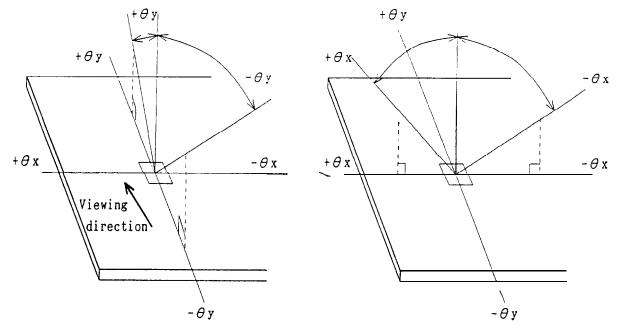

- Note 1) The viewing angle  $\theta$  at which the optimum contrast is obtained by adjusting  $V_{DD}$ - $V_{EE}$ . Refer to Fig.4 for the definition of  $\theta$ .

- Note 2) Max. and Min. values are specified as the Max. and Min. voltage within the condition of operational temperature range  $(0 \sim 50 \text{ °C})$ . Typ. values are specified as the typical voltage at 25 °C.

- Note 3) Display high frequency pattern.

V<sub>DD</sub> = 3 V,V<sub>DD</sub> - V<sub>EE</sub> = 22.0 V, Frame frequency = 85 Hz, Display pattern = 1 bit checker display pattern = 1 bit checker pattern pattern

## 5-2 Input capacitance

Table 5

| Signal   | Input capacitance |

|----------|-------------------|

| s        | 40 pF TYP         |

| CP1,DISP | 250 pF TYP        |

| CP2      | 200 pF TYP        |

| DUO~DU3  | 200 pf TYP        |

| DLO~DL3  | 200 pF TYP        |

| SPEC No. | MODEL No, | PAGE |

|----------|-----------|------|

| LC96211  | LM64K103  | F    |

# 5-3 Interface signals

## Table 6

# OLCD

| Pin No | Symbo 1 | Description                       | Leve 1        |  |  |

|--------|---------|-----------------------------------|---------------|--|--|

| 1      | S       | Scan start-up signal              | "H"           |  |  |

| 2      | CP1     | Input data latch signal           | H→L           |  |  |

| 3      | CP2     | Data input clock signal           | H→L           |  |  |

| 4      | DISP    | Display control signal            | Display on"H" |  |  |

|        |         |                                   | off L         |  |  |

| 5      | VDD     | Power supply for logic and LCD(+) |               |  |  |

| 6      | Vss     | Ground potential                  |               |  |  |

| 7      | VEE     | Power supPlY for LCD (-)          |               |  |  |

| 8      | DUO     |                                   |               |  |  |

| 9      | DU 1    | Display data signal (Upper half)  | H(ON),L(OFF)  |  |  |

| 10     | DU2     |                                   |               |  |  |

| 11     | DU3     |                                   |               |  |  |

| 12     | DLO     |                                   |               |  |  |

| 13     | DL1     | Display data signal (Lower half)  | H(ON),L(OFF)  |  |  |

| 14     | DL2     |                                   |               |  |  |

| 15     | DL3     |                                   |               |  |  |

#### OCCFT

| Pin No | Symbol | Description                      | Level |

|--------|--------|----------------------------------|-------|

| 1      | GND    | Ground line (from Inverter)      |       |

| 2      | NC     |                                  |       |

| 3      | NC     |                                  |       |

| 4      | HV     | High voltage line(from Inverter) |       |

Note) Pin No, and its location are shown in Fig. 10.

OLCD

Used connector: 53261 -151 O(MOLEX)

Mating connector: 51021 -15 OO(MOLEX)

OCCFT

Used connector: M63M83-04(MITSUMI)

Mating connector: M60-04-30-114P(MITSUMI)

M60-04-30-134P(MITSUMI)

M61M73-04(MITSUMI)

LC96211 LM64K103 SHARP CP CP2 <240·637 | Invalid | X  $1.637 \times Invalid$ DU3 5) 2.637 <240·638 | Invalid | 1.638 \Invalid 6) 2.638 X240·639 XInvalid X 1.639 X Invalid X 7) 2.639 1. DUO  $\times 240.640 \times Invalid \times 1.$  $1.640 \times Invalid \times 2.$ 8) 2.640  $\langle 480.637 \rangle$  Invalid  $\langle 241. 1 \rangle$   $\langle 241. \rangle$  $\overline{5}$ (241.637 X Invalid X 242. 242.637 √480.638

✓ Invalid

✓ 241.  $2 \times 241$ 6 X (241.638 XInvalid X 242. 2) 242 • 638 DL1 ⟨480.639 X Invalid X241.  $3 \times 241$ (241.639 X Invalid X 242. 242 • 639  $\langle 480.640 \rangle$  Invalid  $\langle 241.4 \rangle$ 8 (241·640) Invalid X242· [242 • 640] S  $CP2 \times 640/4 \text{ pulses}$ CP1 R DUO-3 1.(1~640) d 240 · (1~640)  $1 \cdot (1 \sim 640)$ (241 · (1~640) DLO~3  $480 \cdot (1 \sim 640)$ (241 · (1~640) CP1  $\times$  240 pulses Fig. 2 Data input timing

SPEC No.

MODEL No.

PAGE

SPEC No. MODEL No. PAGE SHARP LC96211 LM64K103 8 tr CP1 ts12 CP2 DATA CP2 x (640/4) pulses S  $T_{FRM}=8.0^{*1} \sim 16.9 \text{ ms}$ CP1 first second 240th line's line's line's Reduced data data data transfer transfer transfer S CP1 × 240 pulses VIH=0.8 VDD \* 1 See table 7  $V_{IL}=0.2 V_{DD}$ Fig. 3 Interface timing chart

SPEC No.

MODEL No.

PAGE

L C 9 6 2 1 1

L M 6 4 K 1 0 3 | 9

Table 7 Interface timing ratings

| Item                                 | Symbo 1 | Rating |      |           | Unit |

|--------------------------------------|---------|--------|------|-----------|------|

|                                      |         | MIN.   | TYP. | MAX .     |      |

| Frame cycle                          | TFRM    | 8.0*1  |      | 16.9      | ms   |

| CP2 clock cycle                      | Тср2    | 152    |      |           | ns   |

| "H"level clock width                 | tcwn    | 65     |      |           | ns   |

| "L" level clock width                | t C W L | 65     |      |           | ns   |

| "H" level latch clock width          | tiwn    | 70     |      |           | ns   |

| Data set up time                     | tsu     | 50     |      |           | ns   |

| Data hold time                       | t ii    | 40     |      |           | ns   |

| S set up time                        | tssu    | 100    |      |           | ns   |

| S hold time                          | tsıı    | 100    |      |           | ns   |

| CP2↑ clock allowance time from CP1↓  | ts 2 1  | 0      |      |           | ns   |

| CP1↑ clock allowance time from CP2 ↓ | tsı2    | 0      |      |           | ns   |

| Clock rise/fall time                 | tr,tf   |        |      | t r f * 2 | ns   |

\*1: LCD Module functions at the minimum frame cycle of 8 ms (Maximum frame frequency of 125Hz). Owing to the characteristics of LCD Module, "shadowing" will become more eminent as frame frequency goes up, while flicker will be reduced.

According to our exper ments, frame cycle of 11.7 ms Min. or frame frequency of 85 Hz Max. w 11 demonstrate optimum display quality in terms of flicker and "shadowing". But since judgement of display quality is subjective and display quality such as "shadowing" is pattern dependent, it is recommended that decision of frame cycle or frame frequency, to which power consumption of the LCD Module is proportional, be made based on your own through testing on the LCD Module with every possible patterns displayed on it.

\*2:  $t_{rf} = 50$  in case  $t_{cr} = (T_{cP2} - t_{cwh} - t_{cwL})/2 \ge 50$  $t_{rf} = t_{cr}$  in case  $t_{cr} = (T_{cP2} - t_{cwh} - t_{cwL})/2 < 50$

| SPEC No. | MODEL No. | PAGE  |

|----------|-----------|-------|

| T.C96211 | I M64K103 | ່ 1 ∩ |

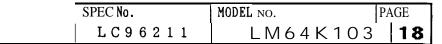

6. Module Driving Method

6.1 Circuit configuration

Fig.9 shows the block diagram of the Module's circuitry.

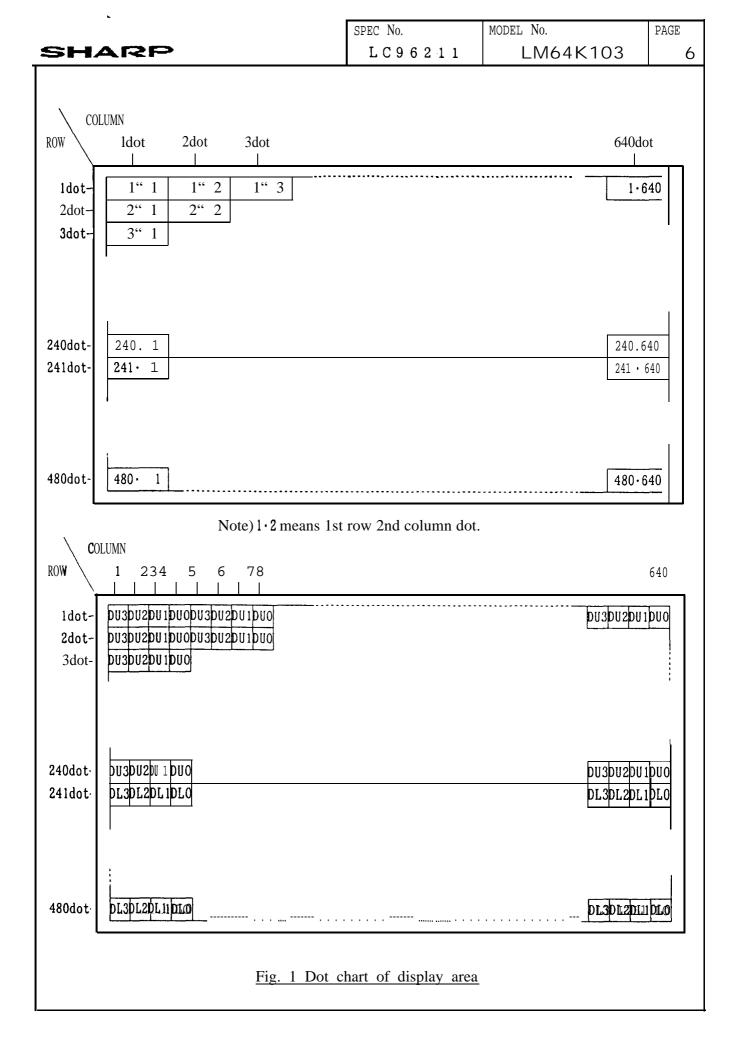

#### 6,2 Display Face Configuration

The display face electrically consists of two (upper and lower) display segments so that the unit may offer higher contrast by reducing drive duty ratio. Each display segment (640x240 dots) is d iven at 1/240 duty ratio.

#### 6.3 Input Data and Control Signal

The LCD driver is 80 bits LSI, cons sting of shift registers, latch circuits and LCD driver circuits.

Display data which are externally divided into data for each row (640dots) will be sequentially transferred in the form of 4-bit parallel data through shift registers by Clock Signal CP2 from the left top of the display face,

When data of one row (640dots) have been input, they will be latched in the form of parallel data for 640 lines of signal electrodes by latch signal CP1. Then the corresponding drive signal will be transmitted to the 640 lines of column electrodes of the LCD panel by the LCD drive circuits,

At this time, scan start-up signal S has been transferred from the scan signal driver to the 1st row of scan electrodes, and the contents of the data signals are displayed on the 1st rows of upper and lower half of the display face according to the combinations of voltages applied to the scan and signal electrodes of the LCD

While the 1st rows of data are being displayed, the 2nd rows of data are entered When 640 dots of data have been transferred then latched on the falling edge of CP1 clock, the display face proceeds to the 2nd rows of display.

Such data input will be repeated up to the 240th row of each display segment, from upper to lower rows, to complete one frame of display by time sharing method. The data input proceeds to the next display face.

Scan start-up signal S generates scan signal to drive horizontal electrodes.

SPEC No.

MODEL No.

PAGE

L C 9 6 2 1 1

LM64K103

11

Since DC voltage, if applied to LCD panel, causes chemical reaction which will deteriorate LCD panel, drive waveform shall be inverted at every display frame to prevent the generation of such DC voltage. Control Signal M plays such role.

Because of the characteristics of the CMOS driver LSI, the power consumption of the Module goes up as the operating frequency CP2 increases. Thus the driver LSI applies the system of transferring 4-bits parallel data through the 4 lines of shift registers to reduce the data transfer speed CP2. Thanks to the LSI, the power consumption of the Module will be minimized.

In this circuit configuration, 4-bit display data shall be therefore input to data input pins of DU<sub>0-3</sub> (upper display segment) and DL<sub>0-3</sub> (lower display : egment).

Furthermore the LCD Module adopts bus line system for data input to min mize the power consumption. In this system data input terminal of each driver LSI activated only when relevant data input is fed.

Data input for column electrodes of both the upper and the lower display segment and chip se ect of driver LSI are made as follows:

The driver LSI at the left end of the display face is first selected, and the adjacent driver LSI of the right side is selected when 80 dots data (20CP2) is fed. This process is sequentially continued until data is fed to the driver LSI at the right end of the display face.

This process is simultaneously followed at the column drivers LSI's of both the upper and the lower display segments. Thus data input for both the upper and the lower display segments must be fed through 4-bit bus line sequentially from the left end of the display face.

Since this graphic display Module contains no ref esh RAM, it requires data and timing pulse inputs even for static display.

The t ming chart of input signals are shown in Fig. 3 and Table 7.

LC96211

LM64K103

PAGE 12

# SHARP

# 7. Optical Characteristics

# $Ta=25 \, ^{\circ}C, V_{DD}-V_{RE}=Vmax$

#### Table 8

Following spec are based upon the electrical measuring conditions, on which the contrast of perpendicular direction ( $\theta x = \theta y = 0^{\circ}$ ) will be MAX.

| Parameter        |                       | Symbol   | Cond                   | ition                 | MIN.           | TYP. | MAX. | Unit | Remark |         |         |

|------------------|-----------------------|----------|------------------------|-----------------------|----------------|------|------|------|--------|---------|---------|

| Viewing          | Trans                 | smissive | <i>Ө</i> х             | Co > 2.0              | <i>θ</i> y=0 " | -25  | -    | 35   | dgr.   | Note 1  |         |

| angle            |                       | mode     | <i>Ө</i> у             |                       | θ x=0 "        | -25  | -    | 30   | dgr.   |         |         |

| range            | Refle                 | ective   | $\theta$ x             | Co > 2.0              | <i>θ</i> y=0 ° | -20  | -    | 35   | dgr.   |         |         |

|                  |                       | mode     | <i>Ө</i> у             |                       | <i>θ</i> x=0 ° | -25  | -    | 25   | dgr.   |         |         |

| Contrast         | Contrast Transmissive |          | со                     | $\theta x = \theta y$ | ·=0 "          | 3.   | 4.5  | -    | -      | Note 2  | Fig.7-3 |

|                  |                       |          |                        |                       |                | 8    | 10   |      |        |         | ig.7-1  |

| ratio Reflective |                       | со       | <i>θ</i> x= <i>θ</i> y | =0 °                  | 2.5            | 4    | -    | -    |        | Fig.7-3 |         |

|                  |                       | _        |                        |                       |                | 6    | 8    |      |        |         | Fig.7-2 |

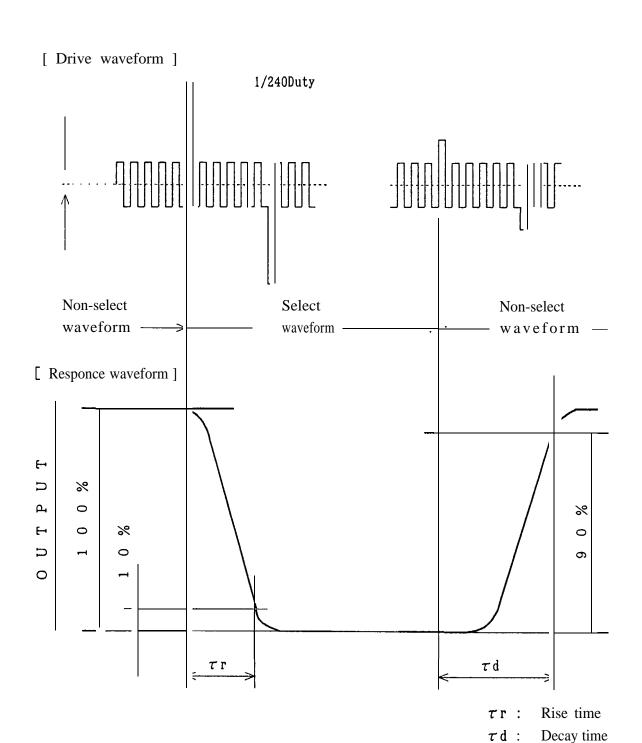

| Response time    |                       | Rise     | aur                    | $\theta x = \theta y$ | =0 °           | -    | 200  | 250  | ms     | Note 3  |         |

|                  |                       | Decay    | τd                     | $\theta x = \theta y$ | =0 ''          | -    | 300  | 350  | ms     |         |         |

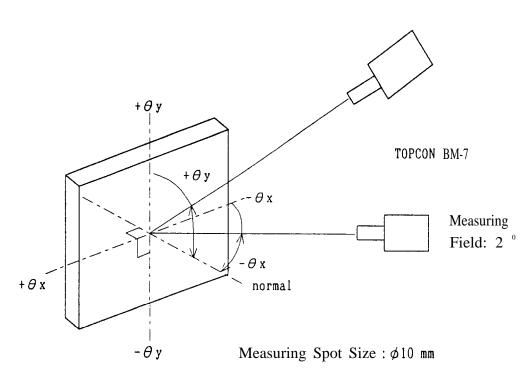

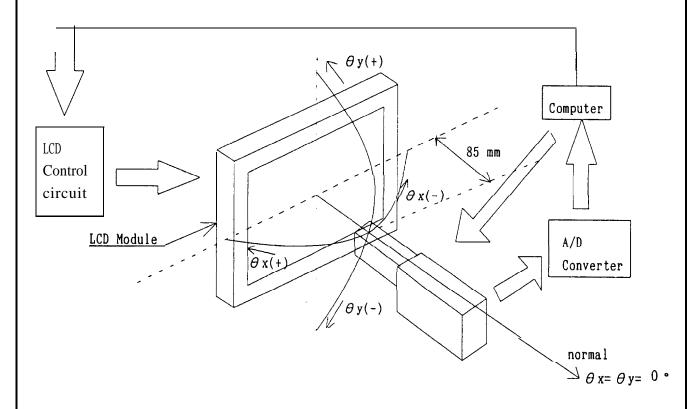

Note 1) The viewing angle range is defined as shown Fig. 4.

Note 2) Contrast ratio is defined as follows:

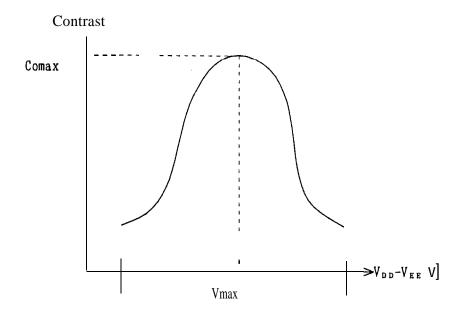

Luminance(brightness) all pixels "white" at Vmax Luminance(brightness) all pixels "dark" at Vmax Vmax is defined in Fig. 6.

Fig. 4 Definition of Viewing Angle

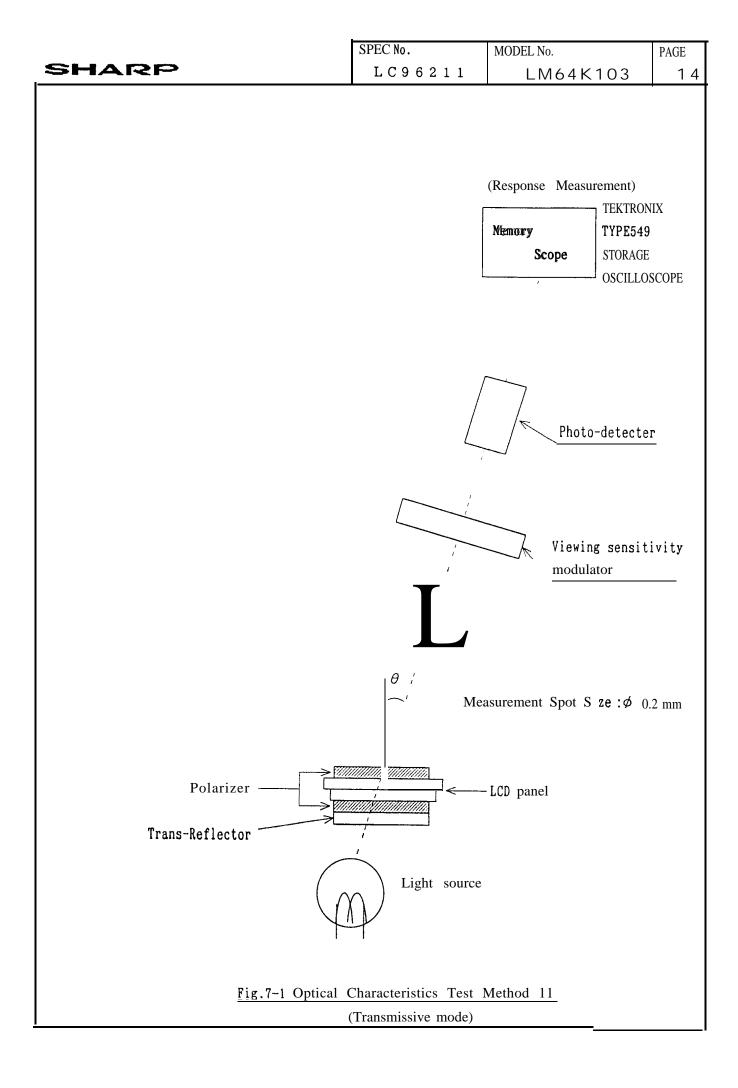

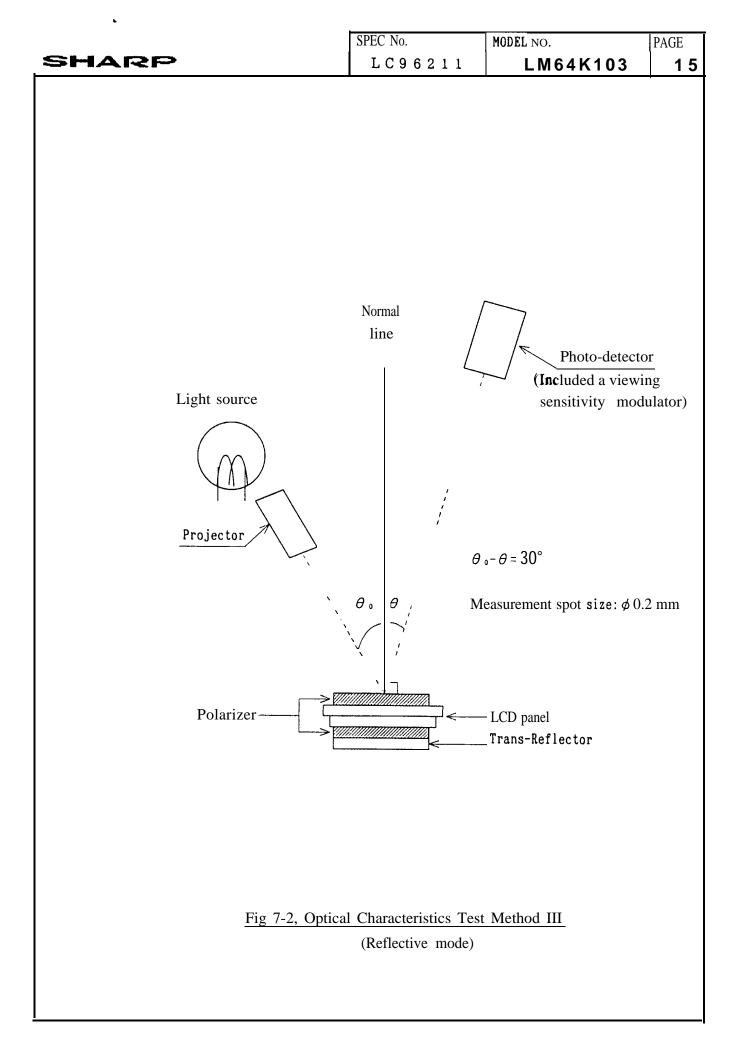

Note 3) The response characteristics of photo-detector output are measured as shown in Fig.7, assuming that input signals are applied so as to select and deselect the dots to be measured, in the optical characteristics test method shown in Fig. 8.

SPEC No.

MODEL No.

PAGE

L C 9 6 2 1 1

LM64K103

13

$\theta$  x : Angle from "normal" to viewing surface rotated about the horizontal axis,

$\theta$  y :Angle from "normal" to viewing surface rotated about the vertical axis.

Fig.5 Optical Characteristics Test Method I

Fig.6 Definition of Vmax

| S | Н | A | 13 | P |

|---|---|---|----|---|

SPEC No.

MODEL NO.

PAGE

L C 9 6 2 1 1

LM64K103

16

(Response Measurement )

Ta=25 "C

In dark room

TOPCON BM7 + quartz fiber

(Measuring Spot Size:  $\phi$  10 mm,

Measuring Field: 2 ")

Fig. 7-3 Optical Characteristics Test Method IV

LC96211

LM64KI03

17

Fig.8 Definition of Response Time

\*1 MG: M GENERATOR CIRCUIT \*2 BG: BIAS GENERATOR CIRCUIT

Fig.9 Circuit block diagram